# Positive Overvoltage Protection Controller with Internal Low R<sub>ON</sub> NMOS FET and Status FLAG

The NCP348 is able to disconnect the systems from its output pin in case wrong input operating conditions are detected. The system is positive overvoltage protected up to +28 V.

Due to this device using internal NMOS, no external device is necessary, reducing the system cost and the PCB area of the application board.

The NCP348 is able to instantaneously disconnect the output from the input, due to integrated Low  $R_{ON}$  Power NMOS (65 m $\Omega$ ), if the input voltage exceeds the overvoltage threshold (6.4 V) or undervoltage threshold, of 3.25 V (UVLO).

At powerup ( $\overline{EN}$  pin = low level), the V<sub>out</sub> turns on 50 ms after the V<sub>in</sub> exceeds the undervoltage threshold.

The NCP348 provides a negative going flag ( $\overline{FLAG}$ ) output, which alerts the system that a fault has occurred.

In addition, the device has ESD–protected input (15 kV Air) when by passed with a 1.0  $\mu$ F or larger capacitor.

### Features

- Overvoltage Protection up to 28 V

- On-Chip Low R<sub>DS(on)</sub> NMOS Transistor: 65 mΩ

- Internal Charge Pump

- Overvoltage Lockout (OVLO)

- Undervoltage Lockout (UVLO)

- Internal 50 ms Startup Delay

- Alert FLAG Output

- Shutdown EN Input

- Compliance to IEC61000-4-2 (Level 4) 8.0 kV (Contact) 15 kV (Air)

- ESD Ratings: Machine Model = B Human Body Model = 3

- 10 Lead WDFN 2.5x2 mm Package

- This is a Pb–Free Device

### Applications

- Cell Phones

- Camera Phones

- Digital Still Cameras

- Personal Digital Applications

- MP3 Players

# **ON Semiconductor®**

http://onsemi.com

= Pb–Free Package

### **ORDERING INFORMATION**

| Device      | Package              | Shipping            |

|-------------|----------------------|---------------------|

| NCP348MTTBG | WDFN-10<br>(Pb-Free) | 3000 / Tape & Reel  |

| NCP348MTTXG | WDFN-10<br>(Pb-Free) | 10000 / Tape & Reel |

<sup>+</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

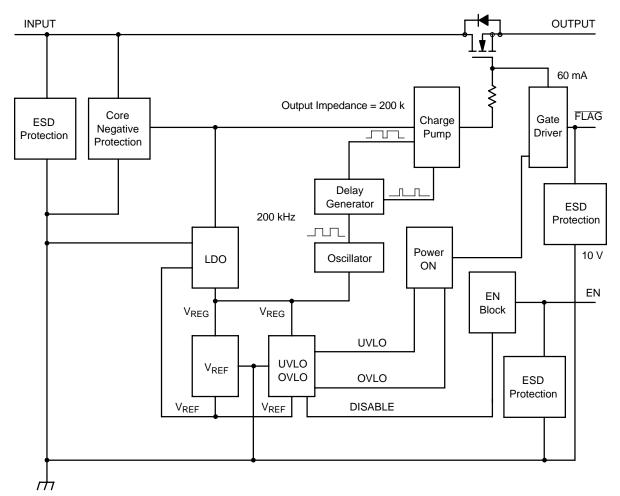

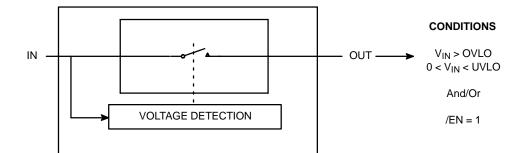

Figure 2. Functional Block Diagram

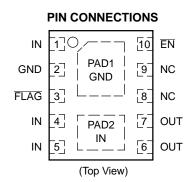

### **PIN FUNCTION DESCRIPTION**

| Pin No. | Symbol | Function | Description                                                                                                                                         |

|---------|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IN     | POWER    | Input Voltage Pin.                                                                                                                                  |

| 4       |        |          | This pin is connected to the power supply.                                                                                                          |

| 5       |        |          | The device system core is supplied by this input.                                                                                                   |

|         |        |          | A 1 $\mu$ F low ESR ceramic capacitor, or larger, must be connected between this pin and GND. The three IN pins must be hardwired to common supply. |

| 2       | GND    | POWER    | Ground                                                                                                                                              |

| 3       | FLAG   | OUTPUT   | Fault Indication Pin.                                                                                                                               |

|         |        |          | This pin allows an external system to detect a fault on IN pin.                                                                                     |

|         |        |          | The FLAG pin goes low when input voltage exceeds OVLO threshold or drop below UVLO threshold.                                                       |

|         |        |          | Since the $\overline{FLAG}$ pin is open drain functionality, an external pull up resistor to $V_{CC}$ must be added.                                |

| 6       | OUT    | OUTPUT   | Output Voltage Pin.                                                                                                                                 |

| 7       |        |          | This pin follows IN pin when "no fault" is detected.                                                                                                |

|         |        |          | The output is disconnected from the V <sub>in</sub> power supply when the input voltage is under the UVLO threshold or above OVLO threshold.        |

|         |        |          | The two OUT pins must be hardwired to common supply.                                                                                                |

| 8       | NC     | OPEN     | No Connect                                                                                                                                          |

| 9       | NC     | OPEN     | No Connect                                                                                                                                          |

| 10      | EN     | INPUT    | Enable Pin.                                                                                                                                         |

|         |        |          | The device enters in shutdown mode when this pin is tied to a high level. In this case the output is disconnected from the input.                   |

|         |        |          | To allow normal functionality, the EN pin shall be connected to GND to a pull down or to a I/O pin.                                                 |

|         |        |          | This pin does not have an impact on the fault detection.                                                                                            |

| PAD1    |        |          | PAD1, under the device. See PCB recommendations page 10.                                                                                            |

|         |        |          | Can be shorted to GND.                                                                                                                              |

| PAD2    |        |          | The PAD2 is electrically connected to the internal NMOS drain and connected to Pins 4 and 5. See PCB recommendations page 10.                       |

### MAXIMUM RATINGS

| Rating                                                                                                                                                                          | Symbol             | Value                              | Unit         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------|--------------|

| Minimum Voltage (IN to GND)                                                                                                                                                     | Vmin <sub>in</sub> | -0.3                               | V            |

| Minimum Voltage (All others to GND)                                                                                                                                             | Vmin               | -0.3                               | V            |

| Maximum Voltage (IN to GND)                                                                                                                                                     | Vmax <sub>in</sub> | 30                                 | V            |

| Maximum Voltage (All others to GND)                                                                                                                                             | Vmax               | 7.0                                | V            |

| Maximum Current (UVLO <v<sub>IN<ovlo)< td=""><td>Imax</td><td>2.0</td><td>A</td></ovlo)<></v<sub>                                                                               | Imax               | 2.0                                | A            |

| Thermal Resistance, Junction-to-Air (Note 1)                                                                                                                                    | $R_{\theta JA}$    | 280                                | °C/W         |

| Operating Ambient Temperature Range                                                                                                                                             | T <sub>A</sub>     | -40 to +85                         | °C           |

| Storage Temperature Range                                                                                                                                                       | T <sub>stg</sub>   | -65 to +150                        | °C           |

| Junction Operating Temperature                                                                                                                                                  | TJ                 | 150                                | °C           |

| ESD Withstand Voltage (IEC 61000–4–2) (input only) when bypassed with 1.0 $\mu$ F capacitor Human Body Model (HBM), Model = 2 (Note 2)<br>Machine Model (MM) Model = B (Note 3) | Vesd               | 15 Air, 8.0 Contact<br>2000<br>200 | kV<br>V<br>V |

| Moisture Sensitivity                                                                                                                                                            | MSL                | Level 1                            | -            |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

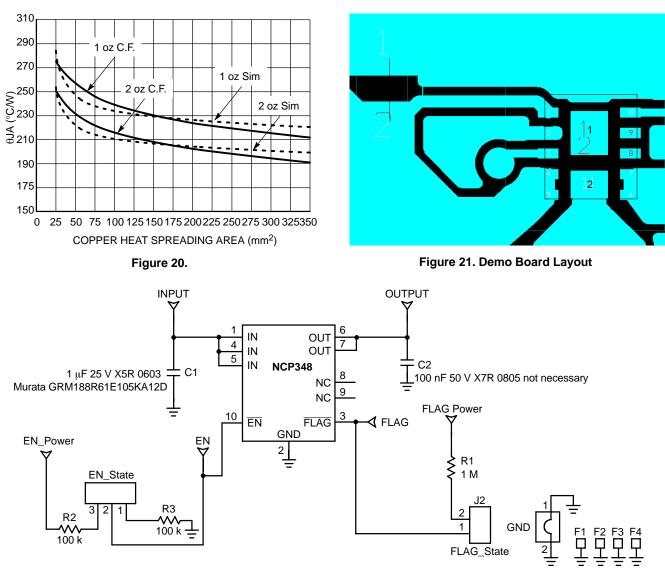

The R<sub>θJA</sub> is highly dependent on the PCB heat sink area (connected to pad 2). As example R<sub>θJA</sub> is 268 °C/W with 30 mm<sup>2</sup> (copper 35 µm) and 189 °C/W with 400 mm<sup>2</sup>.

Human Body Model, 100 pF discharged through a 1.5 kΩ resistor following specification JESD22/A114.

Machine Model, 200 pF discharged through all pins following specification JESD22/A115.

**ELECTRICAL CHARACTERISTICS** (Min/Max limits values ( $-40^{\circ}C < T_A < +85^{\circ}C$ ) and  $V_{in} = +5.0$  V. Typical values are  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| Characteristic                                     | Symbol               | Conditions                                                                              | Min  | Тур  | Мах | Unit |

|----------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------|------|------|-----|------|

| Input Voltage Range                                | V <sub>in</sub>      | -                                                                                       | 1.2  | -    | 28  | V    |

| Undervoltage Lockout Threshold (Note 4)            | UVLO                 | -                                                                                       | 3.00 | 3.25 | 3.5 | V    |

| Undervoltage Lockout Hysteresis                    | UVLO <sub>hyst</sub> | -                                                                                       | 20   | 50   | 100 | mV   |

| Overvoltage Lockout Threshold (Note 4)             | OVLO                 | Vin rises up OVLO threshold                                                             | 6.00 | 6.4  | 6.8 | V    |

| Overvoltage Lockout Hysteresis                     | OVLO <sub>hyst</sub> | -                                                                                       | 50   | 100  | 150 | mV   |

| V <sub>in</sub> versus V <sub>out</sub> Resistance | R <sub>DS(on)</sub>  | $V_{in} = 5.0 \text{ V}, \overline{EN} = GND,$<br>Load connected to $V_{out}$           | _    | 65   | 120 | mΩ   |

| Disable Quiescent Current                          | Idd <sub>dis</sub>   | $V_{in} = 5.0 \text{ V}, \overline{EN} = 1.2 \text{ V},$<br>Load connected to $V_{out}$ | -    | 6.0  | 20  | μΑ   |

| Supply Quiescent Current                           | Idd                  | No load. EN = 5.0 V                                                                     | -    | 90   | 150 | μΑ   |

|                                                    |                      | No load. EN = Gnd                                                                       | -    | 170  | 250 | μA   |

| UVLO Supply Current                                | Idd <sub>uvlo</sub>  | V <sub>IN</sub> = 2.9 V                                                                 | -    | 70   | 100 | μΑ   |

| FLAG Output Low Voltage                            | Vol <sub>flag</sub>  | 1.2 V < V <sub>IN</sub> < UVLO<br>Sink 50 μA on/FLAG pin                                | -    | 20   | 400 | mV   |

|                                                    |                      | V <sub>IN</sub> > OVLO<br>Sink 1.0 mA on FLAG pin                                       | -    | -    | 400 | mV   |

| FLAG Leakage Current                               | FLAGleak             | FLAG level = 5.0 V                                                                      | -    | 1.0  | -   | nA   |

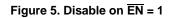

| EN Voltage High                                    | Vih                  | -                                                                                       | 1.2  | -    | -   | V    |

| EN Voltage Low                                     | Vol                  | -                                                                                       | -    | -    | 0.4 | V    |

| EN Leakage Current                                 | ENleak               | $\overline{\text{EN}}$ = 5.0 V or GND                                                   | -    | 1.0  | -   | nA   |

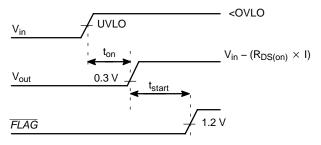

### TIMINGS

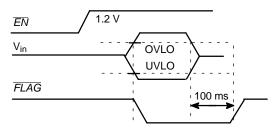

| Startup Delay        | ton    | From V <sub>in</sub> > UVLO to V <sub>out</sub> =<br>0.3 V (See Figures 3 & 7)                                                                                                                                                                            | 30 | 55  | 70  | ms |

|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|----|

| FLAG Going Up Delay  | tstart | From V <sub>out</sub> = 0.3 V to FLAG =<br>1.2 V (See Figures 3 & 9)                                                                                                                                                                                      | 30 | 50  | 70  | ms |

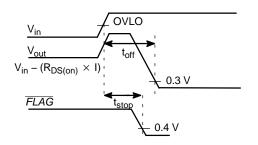

| Output Turn Off Time | toff   | From V <sub>in</sub> > OVLO to V <sub>out</sub> < =<br>0.3 V (See Figures 4 & 8)<br>V <sub>in</sub> increasing from 5.0 V to<br>8.0 V at 3.0 V/μs<br>Rload connected on V <sub>out</sub>                                                                  | -  | 1.5 | 5.0 | μs |

| Alert Delay          | tstop  | $\begin{array}{l} \mbox{From V}_{in} > \mbox{OVLO to } \overline{FLAG} < = \\ 0.4 \mbox{ V (See Figures 4 \& 10)} \\ \mbox{V}_{in} \mbox{ increasing from 5.0 V to} \\ 8.0 \mbox{ V at 3.0 V}  \mbox{s} \\ \mbox{Rload connected on V}_{out} \end{array}$ | _  | 1.0 | _   | μs |

| Disable Time         | tdis   | From $\overline{EN}$ > = 1.2 V to<br>$V_{out} < 0.3 V$<br>Rload = 5.0 $\Omega$<br>(See Figures 5 & 12)                                                                                                                                                    | -  | 1.0 | 5.0 | μs |

NOTE: Electrical parameters are guaranteed by correlation across the full range of temperature.

4. Additional UVLO and OVLO thresholds ranging from UVLO and from OVLO can be manufactured. Contact your ON Semiconductor representative for availability.

### TIMING DIAGRAMS

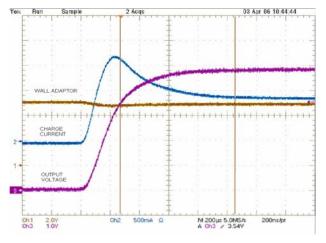

Figure 3. Startup

Figure 4. Shutdown on Overvoltage Detection

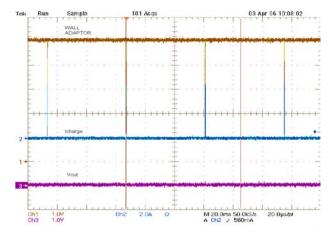

Figure 6.  $\overline{FLAG}$  Response with  $\overline{EN} = 1$

### TYPICAL OPERATING CHARACTERISTICS

### **TYPICAL OPERATING CHARACTERISTICS**

Figure 13. Inrush Current with  $C_{out}$  = 100  $\mu F,$  I charge = 1 A, Output Wall Adaptor Inductance 1  $\mu H$

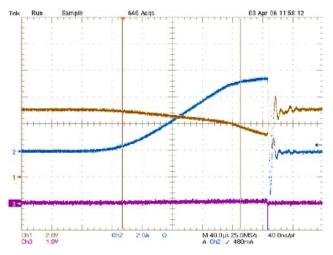

Figure 15. Output Short Circuit (Zoom Fig. 14)

Figure 14. Output Short Circuit

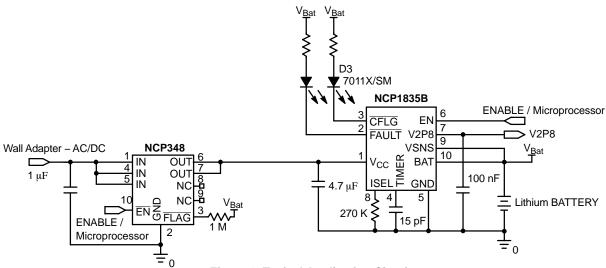

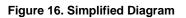

Figure 17. Simplified Diagram

### Operation

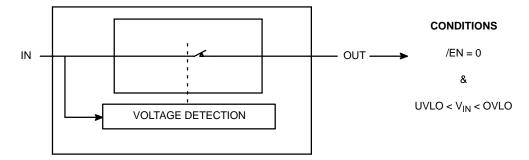

The NCP348 provides overvoltage protection for positive voltage, up to 28 V. A Low  $R_{DS(on)}$  NMOS FET protects the systems (i.e.: charger) connected on the Vout pin, against positive overvoltage. At powerup, with  $\overline{EN}$  pin = low, the output is rising up 50 ms after the input

overtaking undervoltage UVLO (Figure 3). The NCP348 provides a  $\overline{FLAG}$  output, which alerts the system that a fault has occurred. A 50 ms additional delay, regarding available output (Figure 3) is added between output signal rising up and to  $\overline{FLAG}$  signal rising up.  $\overline{FLAG}$  pin is an open drain output.

Figure 18. State Machine

#### Undervoltage Lockout (UVLO)

To ensure proper operation under any conditions, the device has a built-in undervoltage lockout (UVLO) circuit. During  $V_{in}$  positive going slope, the output remains disconnected from input until  $V_{in}$  voltage is below 3.25 V, plus hysteresis, nominal. The *FLAG* output is tied to low as long as  $V_{in}$  does not reach UVLO threshold. This circuit has a 50 mV hysteresis to provide noise immunity to transient condition. Additional UVLO thresholds ranging from UVLO can be manufactured. Contact your ON Semiconductor representative for availability.

#### **Overvoltage Lockout (OVLO)**

To protect connected systems on V<sub>out</sub> pin from overvoltage, the device has a built–in overvoltage lockout (OVLO) circuit. During overvoltage condition, the output remains disabled as long as the input voltage exceeds 6.4 V typical. Additional OVLO thresholds ranging from OVLO can be manufactured. Contact your ON Semiconductor representative for availability.

$\overline{FLAG}$  output is tied to low until V<sub>in</sub> is higher than OVLO. This circuit has a 100 mV hysteresis to provide noise immunity to transient conditions.

### FLAG Output

The NCP348 provides a  $\overline{FLAG}$  output, which alerts external systems that a fault has occurred.

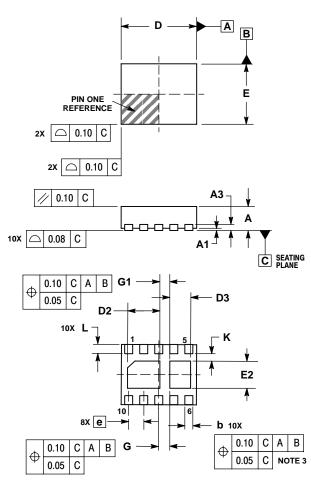

This pin is tied to low as soon the OVLO threshold is exceeded or when the  $V_{in}$  level is below the UVLO threshold. When  $V_{in}$  level recovers normal condition, FLAG is held high, keeping in mind that an additional 50 ms delay has been added between available output and FLAG = high. The pin is an open drain output, thus a pull up resistor (typically 1 MQ, minimum 10 kQ) must be added to  $V_{bat}$ . Minimum  $V_{bat}$  supply must be 2.5 V. The FLAG level will always reflects  $V_{in}$  status, even if the device is turned off ( $\overline{EN} = 1$ ).

### EN Input

To enable normal operation, the  $\overline{EN}$  pin shall be forced to low or connected to ground. A high level on the pin, disconnects OUT pin from IN pin.  $\overline{EN}$  does not overdrive an OVLO or UVLO fault.

#### Internal NMOS FET

The NCP348 includes an internal Low  $R_{DS(on)}$  NMOS FET to protect the systems, connected on OUT pin, from positive overvoltage. Regarding electrical characteristics, the  $R_{DS(on)}$ , during normal operation, will create low losses on  $V_{out}$  pin.

As example:  $R_{load} = 8.0 \Omega$ ,  $V_{in} = 5.0 V$ Typical  $R_{DS(on)} = 65 m\Omega$ ,  $I_{out} = 618 mA$  $V_{out} = 8 x 0.618 = 4.95 V$ NMOS losses =  $R_{DS(on)} x \text{ lout}^2 = 0.065 x 0.618^2 = 25 mW$

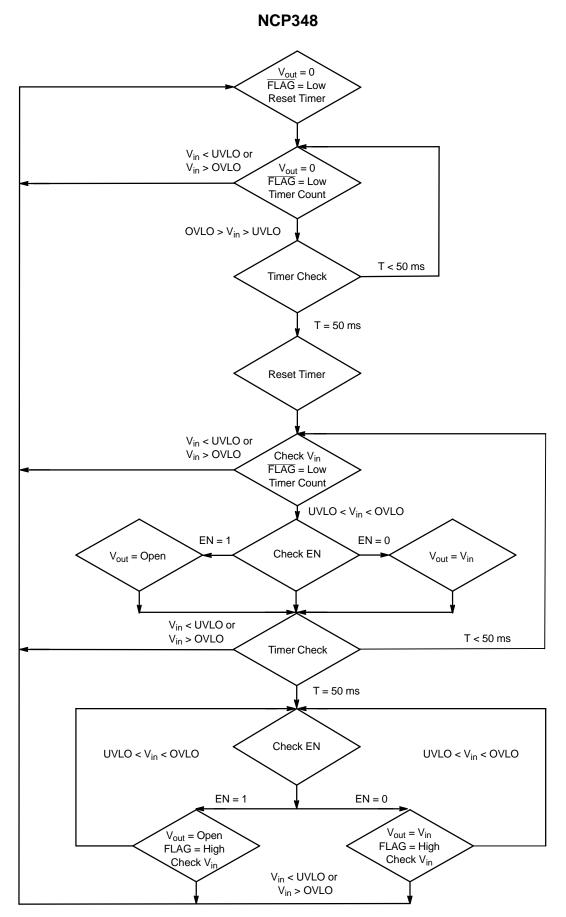

#### **ESD** Tests

The NCP348 input pin fully supports the IEC61000–4–2. 1.0  $\mu$ F (minimum) must be connected between V<sub>in</sub> and GND, close to the device.

That means, in Air condition,  $V_{in}$  has a  $\pm 15$  kV ESD protected input. In Contact condition,  $V_{in}$  has  $\pm 8.0$  kV ESD protected input.

Please refer to Figure 19 to see the IEC 61000–4–2 electrostatic discharge waveform.

Figure 19. Electrostatic Discharge Waveform

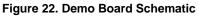

### **PCB** Recommendations

The NCP348 integrates a 2 amperes rated NMOS FET, and the PCB rules must be respected to properly evacuate the heat out of the silicon. The PAD1 is internally isolated from the active silicon and should preferably be connected to ground. The PAD2 of the NCP348 package is connected to the internal NMOS drain and can be used to increase the heat transfer if necessary from an applications standpoint.

Depending upon the power dissipated in the application, one can either use the PCB tracks connected to Pins 4 and 5 to evacuate heat, or make profit of the PAD2 area to add extra copper surface to reduce the junction temperature (See Figure 20). Of course, in any case, this pad shall be not connected to any other potential. Figure 20 shows copper area according to  $R_{\theta JA}$  and allows the design of the heat transfer plane connected to PAD2.

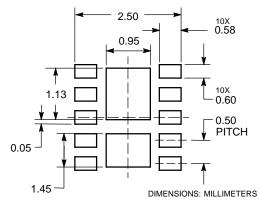

#### PACKAGE DIMENSIONS

WDFN10, 2.5x2, 0.5P CASE 516AA-01 ISSUE A

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: MILLIMETERS.

- 2. CONTROLLING DIMENSION: MILLIMETERS. 3. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN

- 0.15 AND 0.30mm FROM TERMINAL. 4. COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS    |          |      |  |  |

|-----|----------------|----------|------|--|--|

| DIM | MIN            | NOM      | MAX  |  |  |

| Α   | 0.70           | 0.75     | 0.80 |  |  |

| A1  | 0.00           |          | 0.05 |  |  |

| A3  |                | 0.20 REF |      |  |  |

| b   | 0.20 0.25 0.30 |          |      |  |  |

| D   | 2.50 BSC       |          |      |  |  |

| D2  | 0.97           | 1.08     | 1.18 |  |  |

| D3  | 0.57           | 0.68     | 0.78 |  |  |

| е   | 0.50 BSC       |          |      |  |  |

| E   |                | 2.00 BSC |      |  |  |

| E2  | 0.80           | 0.90     | 1.00 |  |  |

| G   | 3.75 BSC       |          |      |  |  |

| G1  | 3.50 BSC       |          |      |  |  |

| K   | 0.20           |          |      |  |  |

| L   | 0.20           | 0.30     | 0.40 |  |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be validated for each customer applications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to rusport or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative